Hi,

We are currently using embOS v4.16 for ARM in an IAR EWARM environment, with the target being a Renesas RZA1H processor.

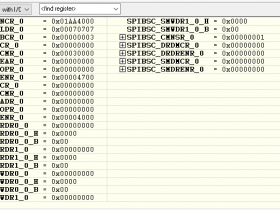

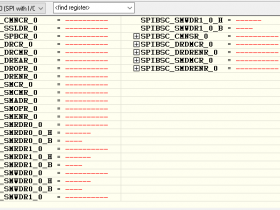

In the file rtosinit_R7S72100.c, in the call to __low_level_init() ,if I

enable the SPI Multi I/O bus controller, add the MMU entries to the translation

table and then call OS_ARM_MMU_Enable(_TranslationTable) I've found that the

registers for the SPI Multi I/O become unavailable.

I have attached 2 images to show the registers before and after enabling the MMU.

Thanks.

We are currently using embOS v4.16 for ARM in an IAR EWARM environment, with the target being a Renesas RZA1H processor.

In the file rtosinit_R7S72100.c, in the call to __low_level_init() ,if I

enable the SPI Multi I/O bus controller, add the MMU entries to the translation

table and then call OS_ARM_MMU_Enable(_TranslationTable) I've found that the

registers for the SPI Multi I/O become unavailable.

I have attached 2 images to show the registers before and after enabling the MMU.

Thanks.